Ivy Bridge Power Saving Technology

If Intel has an obsession at the moment, it’s power consumption. Practically everything we heard at IDF 2011 was about reducing power draw - if it's accompanied by an increase in performance, fine, but mainly it’s all about the power draw. It’s a consequence of wanting ever longer battery life from mobile devices, and ever smaller, slimmer devices with less weight due to large batteries and bulky cooling.If Sandy Bridge was designed primarily as a mobile CPU that happened to be incredibly fast, Ivy Bridge is more so.

Configurable TDP

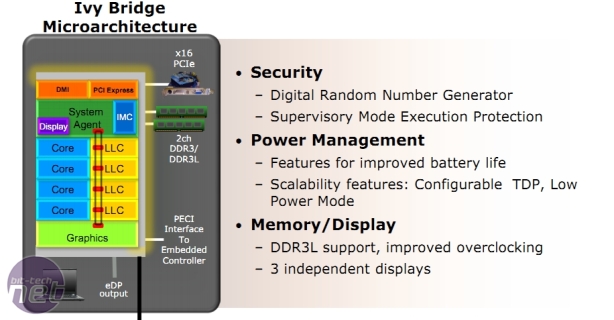

Possibly the most unusual new feature of an Ivy Bridge CPU is its three levels of TDP per CPU. We expect this to be a feature used mostly (possibly exclusively) by ultraportable laptops and ultrabooks, where the ‘TDP Down’ setting is used when the laptop is on the move. The CPU can then use the Nominal or even ‘TDP Up’ setting when it’s got mains power, or when it’s connected to a docking station that increases the amount of cooling for the laptop. Equally, the TDP can be static.

Ivy Bridge features a dynamic TDP based on ‘runtime triggers’, such as whether

its host laptop is running on mains power or not

There’s also a new low power mode in Ivy Bridge, with Intel introducing ‘further optimisations for lower power [at the] lowest active operating point for the part.’ Both of these technologies are of use to anyone building a small desktop machine around Ivy Bridge, but we expect to see them most on thin laptops.

Other Power Draw optimisations

Intel told us that one of the problems with all the fancy power gating and core sleeping technology it’s rolled out over the last few years is that many busses still want to interrupt (wake) Core 0. In fact, the USB bus is notorious for doing this many times a second, even if Core 0 isn’t doing anything and should otherwise be sleeping.It has therefore built in its curiously unhyphenated Power Aware Interrupt Routing (PAIR) technology. Essentially, the CPU is aware of which of its cores are asleep and which are awake, and it prioritises interrupts to wake cores before sleeping ones. This should mean that sleeping cores are left to sleep, saving the power of waking them up just to deal with an interrupt.

We’re sceptical as to how much affect this will have on power consumption, as typically a lot of software is also hard-coded to spam Core 0. If any core is awake, it’s usually Core 0 - open Task Manger and watch it for the next hour or so as you work or browse and you’ll see what we mean.

We were also told that the Ivy Bridge architecture supports lower power consumption choices for the System Agent portion of the CPU. The System Agent is the uncore area of the CPU die that isn’t cache or a communications controller, such as the DMI or PCI-E units. The lower choices of System Agent voltage enables Intel to ‘power optimise low power SKUs [CPUs] further,’ so we expect this to be a feature of the LV and ULV versions of Ivy Bridge processors.

Intel also said that it's introduced design optimisations for greater S3 standby power savings, although it didn’t provide any further details. The company also said that it had optimised the voltage for all the operating frequencies of Ivy Bridge, meaning that the vcore of the CPU is tuned more tightly to the frequency, so that it doesn't waste power while maintaining stability.

Memory improvements (mobile CPUs only)

Finally, Intel has also upgraded the dual-channel DDR3 memory controller of mobile Ivy Bridge to accept ultra-low voltage DDR3, or DDR3L. This is a sensible move, as we found that low-voltage memory is a great way to shave 4-19W from your power draw. That may not sound like much, but some Sandy Bridge CPUs have TDPs well within that range. Another reason for the move was the fact that memory is sometimes mounted on the rear of laptop motherboards, and that DDR3L memory will result in cooler laptop bottoms and human laps. If you want to use DDR3L memory in a desktop system, it’s down to the motherboard to support the low voltages.Intel has also tweaked the memory controller unit of mobile Ivy Bridge CPUs to switch off the DDR I/O to save power when idle, and also switch off the On-Die Termination (ODT) of the memory to reduce peal power consumption.

As well as this, Intel has upgraded the memory overclocking capabilities of the Ivy Bridge memory controller, which we’ll talk about next.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.